Полезные схемы на микроконтроллерах и плис

С чем ассоциируется цифровая электроника? В первую очередь с логическими элементами И, ИЛИ, НЕ. Далее в память приходят сдвиговые регистры, дешифраторы, мультиплексоры и прочее. Однако, по мере роста сложности электронных устройств и тенденции к миниатюризации, создание приборов на базе интегральных микросхем (ИМС) из вышеперечисленных компонентов затруднилось, заказные ИМС нужной топологии и схемотехники оправдывали себя только при крупном тиражировании устройства, в остальных случаях – это было неоправданно дорого.

Выходом из сложившейся ситуации стало развитие программируемых интегральных логических схем (сокращенно – ПЛИС, зарубежная аббревиатура – programmable logic device, PLD). Что это такое и где используется мы расскажем в этой статье.

Отличия от микроконтроллеров

При слове “программируемый” у большинства новичков происходит ассоциация с микроконтроллерами. Не смотря на то что их также программируют, ПЛИС – это совершенно другое устройство.

Для разработчиков в микроконтроллерах доступен фиксированный набор решений и средств присущих конкретному чипу, отступить от архитектуры никаким образом не получится. Вам предоставлен набор команд, с помощью которых вы производите операции взаимодействия с окружающей средой, посредством считывания данных с цифровых и аналоговых входов и отправка сигналов исполнительным устройствам с помощью выходов.

Кроме этого вы можете производить вычисления, сохранять данные в регистрах или ПЗУ, а также оперировать данными прошитыми в память микроконтроллера. На этом в сущности и заключается назначение и особенности работы с микроконтроллерами.

Программируемые логические интегральные схемы (ПЛИС) отличаются тем, что, программируя устройство вы сами создаете архитектуру из базовых логических элементов. Таким образом вы получаете высокое быстродействию и гибкость микросхемы. Это даёт возможность, не изменяя одного чипа сделать целый ряд проектов.

Обобщённо внутреннее устройство ПЛИС можно разделить на три основных группы:

1. Массив из логических элементов (макроячеек, логических блоков).

2. Блоки входа-выхода (IO).

3. Линии связи между ними и устройство, которое управляет этими связями.

Однако такое структурирование очень обобщено, немного подробнее мы рассмотрим этот вопрос ниже.

Программируя вы соединяете элементы подобно тому как бы вы это делали, собирая из отдельных элементов устройство и соединяя их входы и выходы проводниками.

Примечание:

Главным отличием ПЛИС от микроконтроллеров является то, что в микроконтроллере вы не можете изменять внутренних связей между простейшими элементами, а в ПЛИС на основе прописывания связей основывается программирование и работа с ними.

Выбор микроконтроллеров происходит на основе множества критериев, таких как:

Быстродействие и тактовая частота;

Объем ПЗУ и ОЗУ;

Количество входов и выходов.

Другие функциональные особенности и периферии, типа поддержки линий связи и протоколов (I2C, one-wire, PWM-сигнал и прочее).

При выборе ПЛИС основным критерием является количество программируемых блоков – их должно хватить для реализации задачи.

В зависимости от конкретного ПЛИС количество блоков может изменяться в широких пределах, соответственно изменяется и стоимость.

Микроконтроллер выполняет последовательно все операции, прописанные в его программе, в то время как блоки ПЛИС выполняют задачу параллельно и независимо друг от друга, поэтому сравнение этих устройств по тактовой частоте нецелесообразно. Слишком различается их принцип работы.

Виды

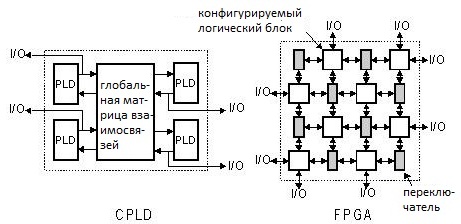

Актуальными на сегодняшний день являются два основных вида ПЛИС:

1. CPLD (Complex Programmable Logic Device – Программируемая Логическая Интегральная Микросхема, собственно это и есть ПЛИС в её классическом понимании). В ней обычно есть встроенная энергонезависимая памятью, в которую загружается прошивка.

Внутренняя структура строится на матрице макроячеек или логических блоков, а количество элементов в них лежит в пределах сотен и тысяч штук. Благодаря относительной простоте стоят дешевле чем следующий вид программируемой логики. Всё это приводит к тому, что используется CPLD в основном в схемах, где нужна высокая скорость и большое число выводов, при этом выполняют несложные задачи.

2. FPGA (Field-Programmable Gate Array – Программируемая Пользователем Вентильная Матрица, однако её часто относят к ПЛИС) – более развитые и сложные устройства по сравнению с CPLD, строятся на логических блоках с гибкой коммутаций и содержат большее число элементов (десятки или сотни тысяч штук).

Прошивка, как правило, хранится во внешней энергонезависимой памяти. Кроме простейших логических элементов в FPGA могут содержаться готовые блоки для выполнения каких-либо операций, например, блоки обработки сигнала DSP. Всё это позволяет реализовать процессор, устройства обработки сигналов и другие сложные устройства.

Интересно:

Хотя фактически наличие энергонезависимой памяти не делает программируемую логику CPLD. Это частично заблуждение. Главным отличием CPLD от FPGA является внутренняя структура.

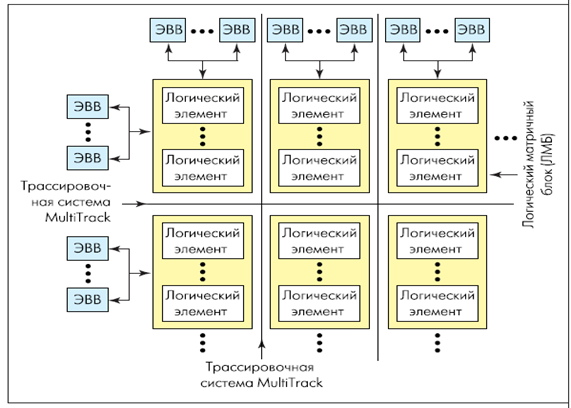

Подробнее внутреннее устройство CPLD изображено на рисунке ниже.

А примерная схема её макроячейки выглядит таким образом:

Макроячейка состоит из программируемых мультиплексоров, триггеров (одного или нескольких) и формирует группу выходных сигналов ФБ в нескольких их вариантах.

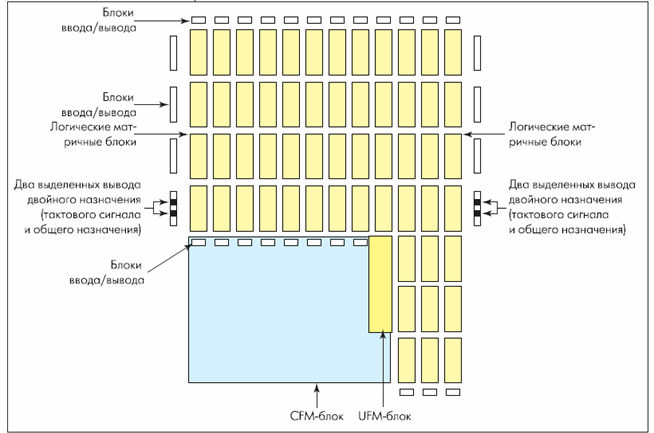

Ниже приведен еще один пример – блок-схема CPLD микросхемы семейства MAX II фирмы Altera.

И структурный план микросхем этого же семейства.

Промежуточные шины макроячейкам назначаются с помощью такого узла, как распределитель, на англ. он звучит как Logic Allocator, что изображено на схеме ниже, на ней же изображена матрица переключений (Global Routing Pool), а у выходных макроячейки (macrocells) имеют по две обратных связи.

Внешние выводы микросхемы соединяются с выходами макроячеек через еще один блок (матрицу) – ORP (Output Routing Pool), обратите внимание, что через неё же происходит соединение ВХОДНОЙ логики с GRP, что изображено на иллюстрации ниже.

Примечание:

В некоторых CPLD есть т.н. прямые входы (Direct Input) – они соединены со входами ячеек напрямую, что уменьшает задержки.

У FPGA структура имеет вид:

L – логический конфигурируемый блок;

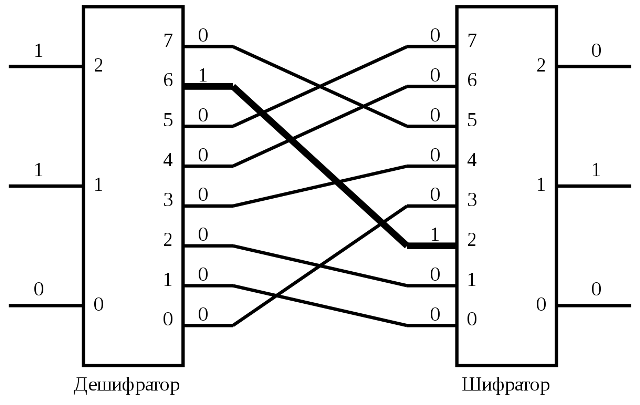

S (substitution block) – блок подстановок, он получает на ход определенное число бит, преобразует, по определенному алгоритму, а на выходе выдаёт другое число бит. Другими словами – дешифратор, шифратор и коммутатор.

C (connection block) – блок соединений.

Схема S-блока:

Программирование

HDL (Hardware Description Language, рус. Язык описания аппаратуры) – так называется язык с помощью которого программируются ПЛИС. Популярными и универсальными являются Verilog HDL и VHDL. Существуют и другие языки, например, присущие конкретным производителям, как AHDL для изделий компании ALTERA.

Разработчикам, которые работают с ПЛИС доступно графическое программирование. То есть вы можете просто рисовать логические схемы или комбинировать код с графикой. Последнее называют модульным методом разработки, когда конкретные модули прописываются, а верхний модуль, в котором всё объединяется программируется графическим способом.

Примеры популярных производителей и серий

На момент написания статьи наиболее известными являются изделия двух производителей.

Altera (основана в 1983 году);

Xilinx (Основана в 1984 году).

У Altera есть несколько основных серий программируемой логики:

MAX, MAX II, MAX IIZ;

7000S;

3000A;

MAX V;

Cyclone;

Arria;

Stratix.

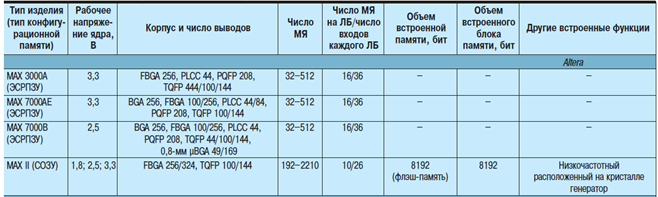

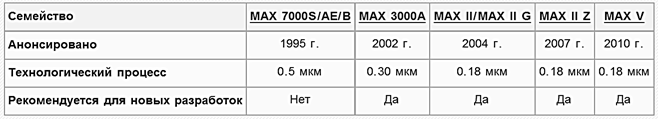

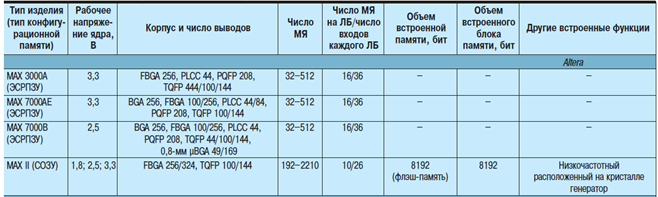

Рассмотрим каждый из них подробнее. В таблицах ниже вы видите общие сведения о микросхемах семейства.

CPLD фирмы Altera 3 CPLD:

MAX – это CPLD для использования в мобильных устройствах, отличительными чертами является относительно малое энергопотребление и тепловыделение. В зависимости от сложности и годов выпуска различают следующие модификации:

7000S на сегодняшний день устарела, она выпущена в 1995 году.

3000A – выпущена в 2002 году, производится по 300нм технологии. Состоит из небольшого числа макроячеек (32-512)

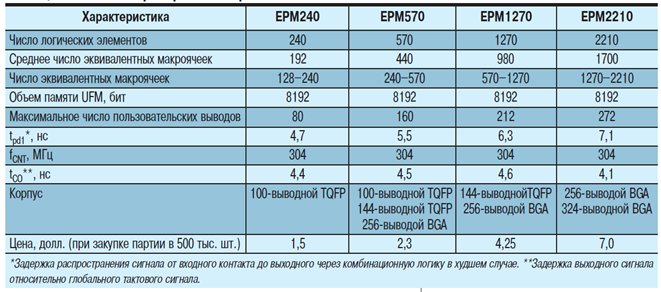

MAX II выпущена в 2004 году, производится по 100нм технологии, состоит из большего числа блоков (240-2210), работающих на частоте до 304МГц. Изделие выполняется в корпусах типа TQFP 0.5 mill со 100 и более ножек.

MAX IIZ – 2007 года, основной особенностью является пониженное энергопотребление – это положительный момент, однако и частоты понижены до 152МГц. Питание данных микросхем осуществляется от 1.8 В.

MAX V – 2010 год. Производится по технологии 180нм, может содержать от 40 до 2210 блоков и работать на частотах до 152МГц или на 304МГц – это зависит от количества блоков.

FPGA:

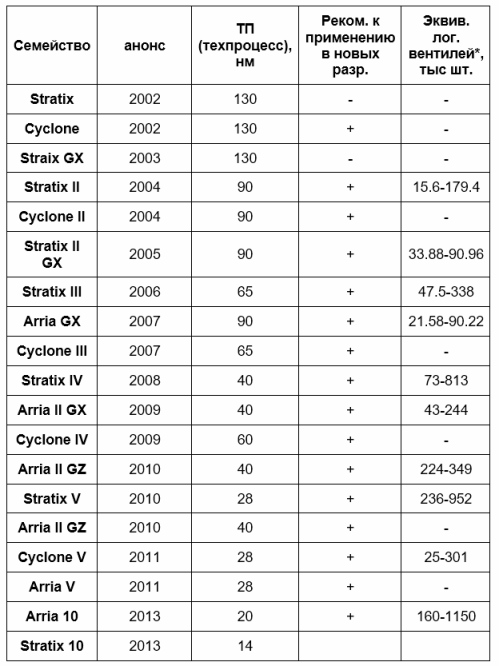

Cyclone – это уже бюджетные микросхемы типа FPGA. Различаются пять поколений, которые маркируются греческими цифрами (от I до V соответственно). Первое поколение выпущено в 2002 году, производилось по 180нм технологии, а пятое поколение вышло в 2011 году и производится по 28нм технологии. Стоит отметить что все поколения остаются актуальными.

Arria – также относятся к FPGA среднего уровня.

Stratix – мощные FPGA.

Ниже приведены сводные таблицы по программируемой логике FPGA от компании Altera.

И полная таблица по ссылке: https://electrik.info/tablitsa.docx

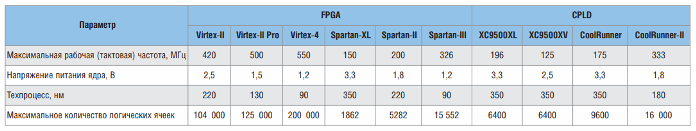

У производителя Xilinx CPLD представлены сериями:

XC9500XL из 36-288 макроячейках. Работают на частотах до 178МГц, а модели на 288 макроячеек на 208МГц. Выполняется как в небольших корпусах с 44 пинами (выводами) на расстоянии 0.8 мм друг от друга – такие корпуса считаются легкопаяемыми. Также бывают и с 64 и со 100 ножках с шагом в 0.5 мм, а также моделями в корпусах типа PLCC.

Серия CoolRunner-II – это энергоэффективные, но производительные CPLD. Особенностью является питание от напряжения в 1.8В, входы-выходы рассчитаны на работу в диапазоне 1.5-3.3В. Состоят из 32-512 макроячеек и производятся по 180нм технологии. В зависимости от количества ячеек работают в диапазоне частот 179-323МГц, при этом чем меньше ячеек – тем с большей частотой они могут работать в этом случае. Встречаются в разных корпусах, в том числе легкопаяемых, как в микросхемах рассмотренной выше серии.

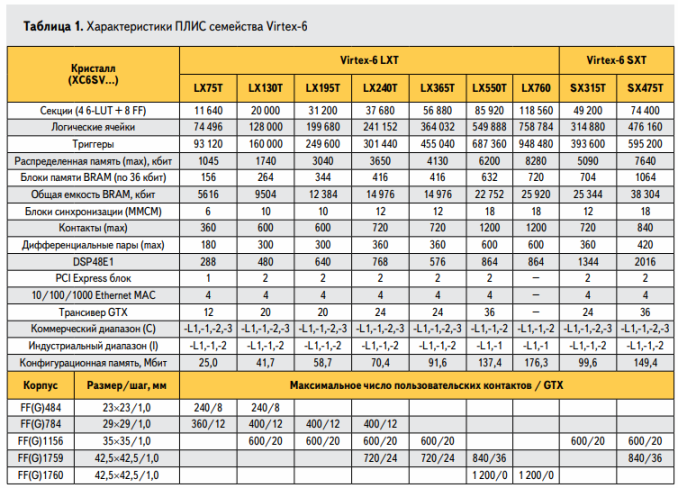

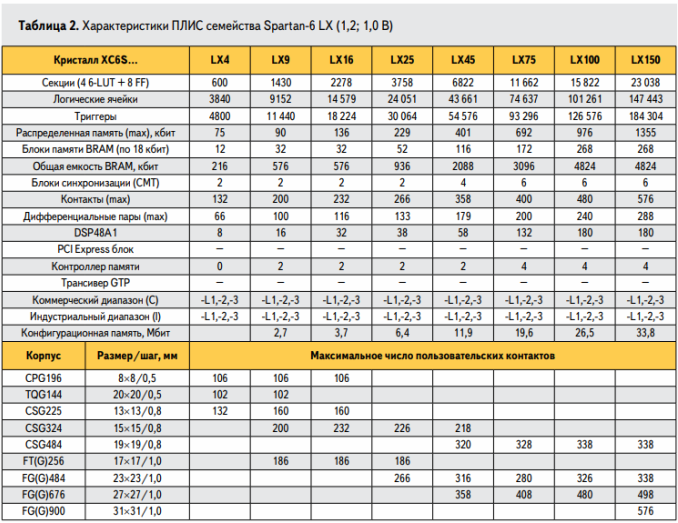

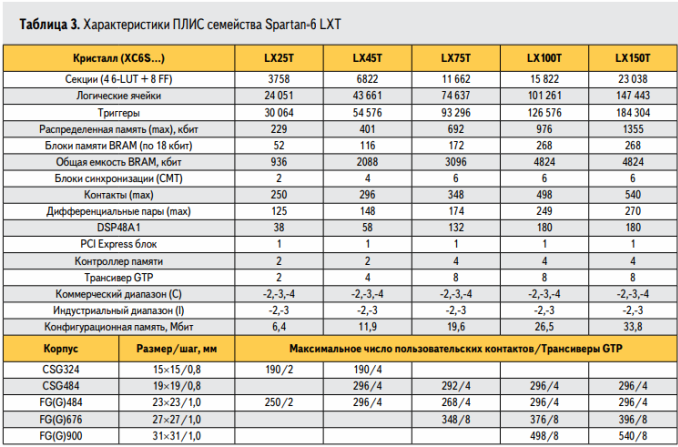

Компания Xilinx не обошла стороной и FPGA:

Spartan-6 – состоят из 6-входовых логических блоков, их количество лежит в пределах 3840-147443 штуки. Интересны тем что могут содержать контроллеры для обмена данными типа DDR2, DDR3, PCI-EXPRESS, Ethernet 1Gbit, SerialATA etc…

Серия Vitrex-7 отличается сложностью, микросхемы могут содержать до 2 000 000 логических блоков и 1200 контактов.

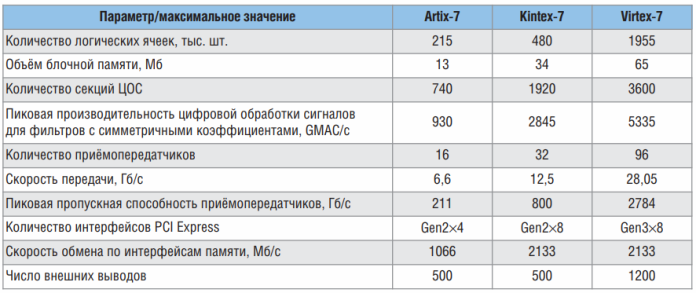

Ниже вы можете ознакомиться со сводными таблицами с характеристиками CPLD и FPGA от Xilinx 6 и 7 серии, а также Zynq-7000.

Заключение

ПЛИС и ППВМ производится и другими компаниями такими как Lattice Semiconductor (в 2002 году начала производить FPGA), Actel и небезызвестный читателям нашего сайта своими микроконтроллерами ATMEL и многие другие. На программируемой логике можно реализовать ряд устройств, в одном устройстве реализовать параллельные независимые друг от друга вычисления, однако для домашних проектов часто их покупка является финансово неоправданной, но при этом довольно разумна в производственных масштабах, как альтернатива заказным интегральным схемам.

Алексей Бартош

P.S. Посмотрите видео, в нём вы увидите пример реализации игровой приставки Nintendo на FPGA:

Источник

ВВЕДЕНИЕ

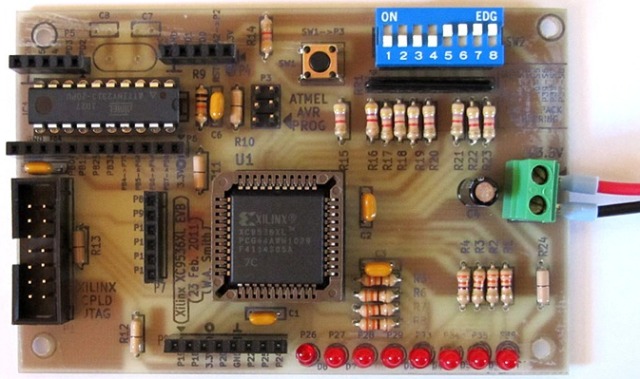

Обычно, когда кто-то видит функционирующую плату, всегда задают одни и те же вопросы: – Это Ардуино? – А как это работает без Ардуино?

Это не микроконтроллер, это даже не процессор, это ПЛИС. ПЛИС – это программируемая логическая интегральная схема, такая микросхема состоит из множества одинаковых блоков или макроячеек, каждый производитель по своему их называет, так у Xilinx это Slices (ломтики) у Altera – LogicElements (логические элементы). Эти блоки относительно простые, они могут выполнять роль нескольких логических элементов, быть маленькой таблицей поиска (LUT), содержать готовый сумматор, умножитель, блок цифровой обработки сигналов (DSP), в общем все что задумает производитель. Пользователь может по своему желанию расположить и настроить эти блоки как ему захочется, реализовав таким образом достаточно сложные цифровые схемы. На ПЛИС можно реализовать хоть микроконтроллер, реализовав например ту же Ардуино или процессор вашей собственной архитектуры, например не регистровый а стековый процессор, даже свою собственную ПЛИС можно реализовать на ПЛИС!

Из доступных бюджетных ПЛИС можно выделить двух основных производителей Altera и Xilinx, с их продукции можно начать свой путь освоения данных технологий. На мой взгляд лучше выбрать чипы компании Altera, так как их среда проектирования стабильно обновляется, а выбрав один популярный чип Xilinx XC3S500E вам придется довольствоваться устаревшей средой ISE 14.7 (хотя и там есть свои плюсы).

В иностранной литературе можно встретить сокращения для ПЛИС: FPGA и CPLD. CPLD (Complex Programmable Logic Device ) – чипы с небольшим числом макроячеек, специализированных блоков и малым энергопотреблением. Большой проект не получится синтезировать для такого типа чипов, но и для них находят применение на практике, так у редкого микроконтроллера найдется, скажем 300 ножек. Такие чипы часто применяют в качестве интерфейсных систем, предобработчиков, расширителей ввода-вывода. FPGA (Field-Programmable Gate Array) – программируемая пользователем вентильная матрица (ППВМ), значительно более мощные чипы по сравнению с CPLD, но потребляющие больше энергии и стоящие значительно дороже. Для уменьшения затрат площади кристалла FPGA чипы могут содержать уже готовые функции, такие как блоки цифровой обработки сигналов (DSP блоки), встроенные процессоры, встроенная память. FPGA широко применяются для проверки и верификации проектов, в так называемой докремниевой проверке пригодности, тем самым уменьшая затраты и время перед выходом продукта. FPGA чипы могут быть переконфигурированы практически в любой момент времени, сейчас ведутся разработки, например в Intel, по совмещению архитектур обычного процессора и чипа FPGA. У Xilinx уже есть такие решения – Zynq, но о них мы пока не будет вести речь.

Разговор пойдет о более простых вещах, тем более ко мне в руки попал набор разработчика: Cyclone IV 4 FPGA Core Board и Altera USB Blaster Downloader PLD Development kit за 35$, приобретенный на AliExpress.

1 Демоплата Cyclone IV 4 FPGA Core Board, краткая характеристика

Рис. 1 – Демоплата Cyclone IV 4 FPGA Core Board

На плате (Рис. 1) установлен чип EP4CE6E22C8N, его характеристики:

| Вид ресурса | Краткое описание | Количество |

|---|---|---|

| Logic elements (Les) | Число логических блоков – ячеек, основная характеристика, по которым мы можем сравнивать «мощность» чипов, любая синтезированная логика будет затрачивать данные блоки | 6,272 |

| Embedded memory (Kbits) | Встроенной памяти, пока для нас не важная характеристика | 270 |

| Embedded 18×18 multipliers | Встроенных аппаратных умножителей, очень важный параметр в цифровой обработке сигналов, вся мощь ПЛИС раскрывается, когда несколько умножителей работают параллельно | 15 |

| General-purpose PLLs | Узлов фазовой автоподстройки частоты, пока не важная характеристика, упрощает синхронизацию устройств, работающих на разных частотах | 2 |

| Global Clock Networks | Количество частотных доменов, пока не важная характеристика | 10 |

| User I/O Banks | Число раздельных пользовательских банков ввода-вывода, пока не важная характеристика | 8 |

| Maximum user I/O | Число пользовательских пинов ввода-вывода, мы можем подключить любые устройства, как например к Ардуино | 91 |

На плате установлено:

- Флэш память – при подаче питания ПЛИС будет сконфигурирована в реализацию во флеш памяти. Вы можете синтезировать свой проект и записать в эту флэш

- Кварц 25 Мгц – генератор опорной тактовой частоты, именно на этой частоте будут работать все наши проекты, наша ПЛИС может поддерживать до 10 таких каналов.

- Светодиоды – 10, кнопки – 2.

- Пины ввода-вывода 61 + 2 земля, 1 не соединен. Можно подключить разнообразные устройства. ЦАП-АЦП, акселерометры и гироскопы, символьный и графические дисплеи, как и у Ардуино.

- Питание через USB, или внешнее 5В.

В комплекте также идет программатор JTAG, Altera USB Blaster.

2. Среда Quartus II и наш первый проект

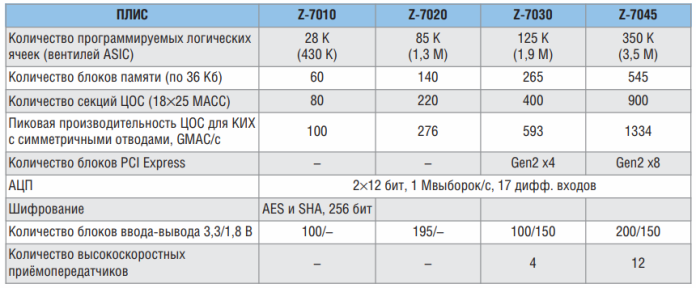

Для работы с данной ПЛИС нам нужно скачать официальную среду разработки – Quartus II Web Edition, она бесплатная. Заходим на официальный сайт https://dl.altera.com/15.0/?edition=web, на момент написания версия 15.0 самая новая, если вышла новее, скачиваем ее.

Выбираем:

Рис. 2 – выбираем необходимые продукты Altera

И жмем кнопку скачать (Download Selected Files). После чего нам предложат зарегистрироваться, регистрируемся, скачиваем и устанавливаем.

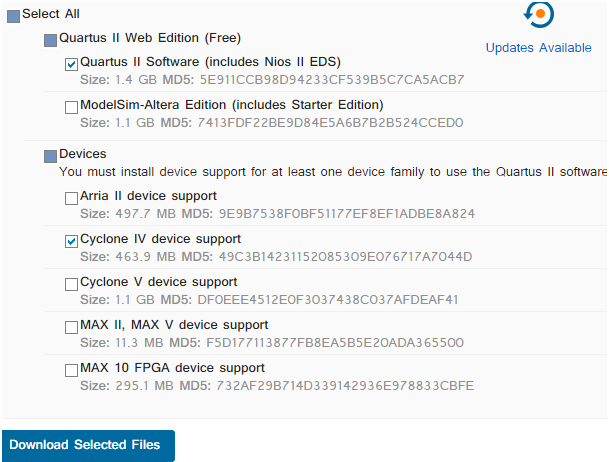

Создадим свой первый проект.

Запускаем Quartus, выбираем главное меню File -> New Project Wizard, появляется окно введения, жмем next. Далее нужно указать каталог для проекта и его имя, третье поля – имя верхнего модуля, попозже увидите, что это. Выбираем папку, куда хотим сохранить проект и придумываем имя, у меня test1.

Рис. 3 – окно мастра нового проекта

Жмем next, у нас спрашивают, пустой проект (empty project) или шаблон (Project template). Оставляем пустой, next. Дальше нас просят добавить существующие файлы, у нас ничего нет, поскольку мы только начинаем свой путь, жмем next.

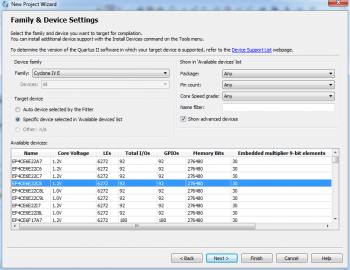

Далее нам необходимо выбрать наш чип, это можно сделать в любое время. Выбираем как на рисунке, Family – Cyclone IV E, specific device selected in “Available devices” и выбираем наш чип EP4CE6E22C8N, он в самом начале. Если у вас другой, найдите свой, это важно. Жмем next.

Рис. 4 – Окно мастера нового проекта, выбор нужного чипа

Появится окно – выбора средств проектирования, отладки, пока это пропускаем, нажимаем next и затем finish.

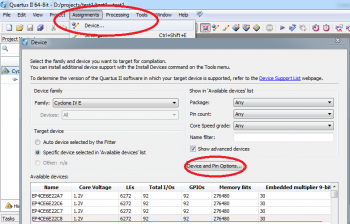

Далее главное меню Assignments -> Device, здесь можно выбрать чип (нашу ПЛИС), выбираем если не выбрали, нажимаем кнопку «Device and Pin Options».

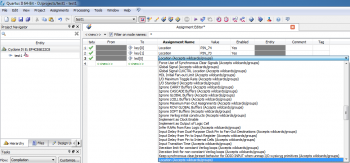

Рис. 5 – Окно «Assinments-Deice»

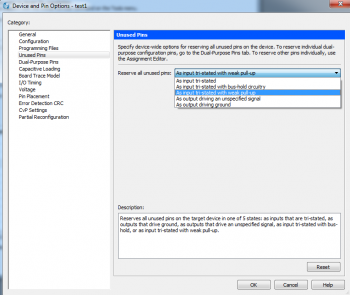

В окне выбираем пункт «Unused pins». Эта настройка определяет, что будет с неподключенными пинами. Это может быть важно, в своем проекте вы вряд ли используете все пины, а не подключенные могут быть на деле соединены с землей или питанием (ну мало ли, кто разводил плату). Если вы подадите единичку на заземленный пин, то он сгорит, поэтому нужно внимательно следить за этим.

По умолчанию неиспользуемые пины «As input tri-stated with weak pull-up» (пины для ввода, находятся в третьем состоянии с высоким импедансом, со слабой подтяжкой по питанию), можно оставить или выбрать «As input tri-stated». Про подтягивающий резистор можете прочитать на википедии https://ru.wikipedia.org/wiki/Подтягивающий_резистор. В цифровой технике может быть три состояния, логическая единица – это напряжение питания или высокий уровень, логический ноль – это когда вывод подключен к земле или низкий уровень и высокоимпедансное состояние. Высокоимпедансное состояние – это когда пин имеет очень высокое сопротивление и практически не влияет на провод, к которому подключен, такое состояние нужно, например, при организации шин, когда множество устройств подключены к одному проводу и не активные устройства не мешают работе.

Рис. 6 – Окно «Device and Pin Options», Unused Pins

Далее нам нужно настроить пины, это нужно чтобы сигнал шел на нужные нам ножки чипа, ведь изначально Quartus не знает, что куда подключено и как именно осуществлена разводка платы.

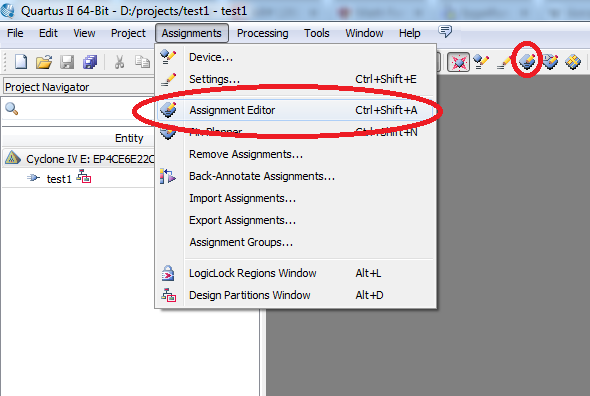

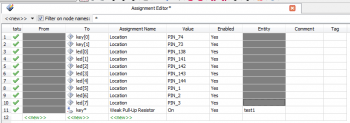

Подключаем это все в «Assignment Editor»

Рис. 7 – Вызов «Assignment Editor» из меню или панели

В появившемся окне делаем как у меня, ну или если совсем правильно, то согласно схеме вашей платы.

Рис. 8 – Assinement Editor

В колонке «To» вписываем имя входа или выхода. В колонке «Assignment Name» выбираем «Location». В колонке «Value» номер контакта микросхемы, согласно схемы платы (у меня номера пинов написаны прямо на плате).

Также нужно указать, что делать с кнопками, которые одной ногой подключены к земле, а другой ко входу чипа. При нажатии на ноге будет низкий уровень, а вот без нажатия, непонятно, нога чипа будет просто висеть в воздухе, что очень плохо. Нужно подтянуть к питанию вход чипа либо резистором на плате, либо боле элегантным способом в «Assignments Editor». В колонке «Assignment Name» выбираем «Weak Pull Up resistor» для группы key* (группа обозначается через звездочку).

Рис. 9 – Assignment Editor

Нажимаем сохранить.

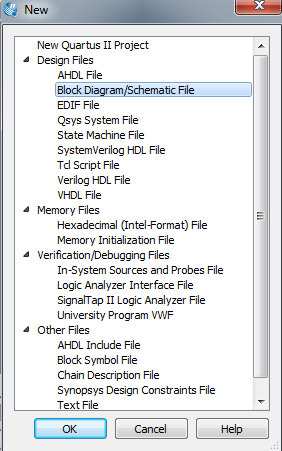

Далее нужно создать описание модуля верхнего уровня, который будет работать непосредственно с ножками чипа, все остальные модули будут работать только с ним. В главном меню жмем New, и выбираем “Design Files-> Block Diagram/Schematic File”.

Рис. 10 – Диалог новых файлов

В открывшемся окне выбираем инструмент «Pin Tool» и располагаем вход и выход (пины ввода и вывода) на диаграмме. Переименовываем вход как key[0], выход как led[0] и соединяем их проводником. Сохраняем и нажимаем “Start Compilation”.

Рис. 11 – Окно графического описания, выделены Pin Tool и Start Compilation

После компиляции у нас возникли предупреждения, пока игнорируем их, они касаются неподключенных пинов, отсутствия тактового сигнала и описания для «Timing Analyzer».

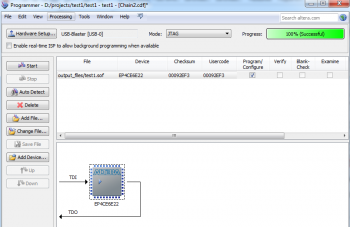

Подключаем демоплату и программатор, выбираем инструмент «Programmer». В окне должно значиться «USB-Blaster [USB-..]», если нет то нажимаем «Hardware Setup» и пытаемся разобраться почему нет, скорее всего не установлены драйвера, смотрим в устройства Windows, ищем неопределенные устройства, может с кабелем проблема. Если все хорошо нажимаем «Auto Detect» и выбираем наш чип.

Рис. 12 – Окно Programmer

Нажимаем двойным щелчком мыши в поле «File» и выбираем файл для записи на ПЛИС (находиться в папке output_files нашего проекта), ставим галочку в поле «Program / Configure», и нажимаем кнопку «Start».

Рис. 13 – Окно Programmer, наш чип уже сконфигурирован

Поздравляю с первой конфигурацией ПЛИС! Диод D1 должен светиться, при нажатии key1 должен гаснуть (так как кнопка замыкает ножку с землей), далее мы с этим что-нибудь сделаем)

Вторая часть

Теги:

Источник